请点击上面蓝字,收阅菁英EDA

By菁英EDA(微信最好的芯片IC版图设计、封装PKG设计和线路板PCB 设计全EDA设计链的学习读物,以专业的视角传递EDA最新信息)

微信号:EDA_Hunter

关注我,了解更多的EDA设计技术,问题或建议,请添加我微信

作者:晨晞

主要分享EDA设计的学习资源、面试技巧、职场现象,帮助快速了解EDA设计行业,帮助想转行、进阶、小白成长为高阶EDA工程师。

如果你觉得公众号对你有帮助,欢迎推荐给他人..

感谢您抽出

阅读本文

IQ的是Intelligence Quotient的缩写,中文翻译为智商或智力商数,系个人智力测验成绩和同年龄被试成绩相比的指数,也是衡量个人智力高低的标准。EDA设计中也有自己的IQ,不仅有IQ,还有EQ,是不是很有趣?

其实,EDA设计中的IQ是指的一种射频调制模式信号的名字简称,I是In-phase的首字母,表示同相,Q是Quadrature 表示正交,与I相位差90度。

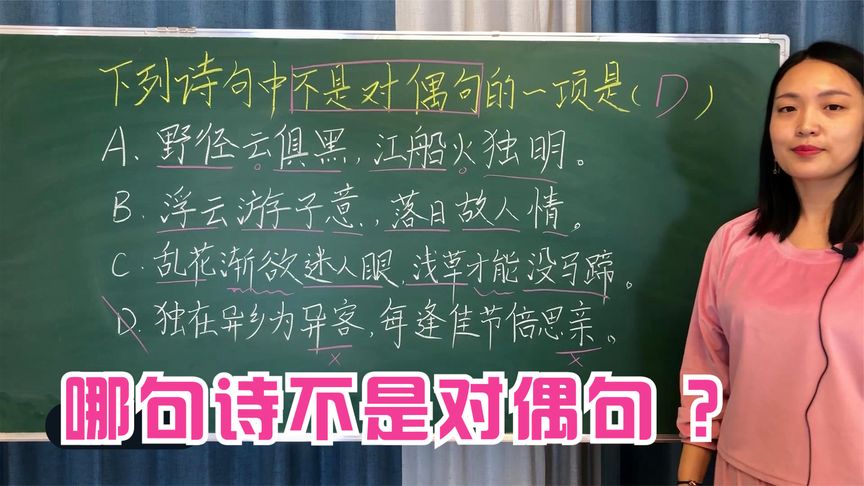

如下图所示,是CPU和Transcevier(收发器)之间的3组IQ线,看最上面的AK2、AK3、AL3和AK4引脚,其中I有RF_TX_BBIP和RF_TX_BBIN,Q有RF_TX_BBQP和RF_TX_BBQN,这4根线就组成了一组IQ线。

IQ线用在哪些电路中?

IQ做为一种调制模式,经常在射频电路中使用,手机电路中射频电路一般有WIFI、2G、4G、5G、RFID、NFC、IR、GPS、BT和FM,其中在GPS、WIFI和Transcevier上使用的较多,如下图所示。

下图是WIFI、GPS、BT和FM四合一的MT6225方案的IQ线连接图,WB中W代表WIFI,B代表BT,WB共用2对IQ线,另外1对给GPS使用,红色方框内所示;

IQ线的规划布局

IQ信号线走线非常重要,如果在传输过程中出现了干扰和畸变,就会造成信号传输错误,因为IQ信号本质上是一个模拟信号,所以IQ信号线的隔离和保护对EDA工程师来说必须要提前布局好!

IQ线在手机布局和规划走线时必须保证远离大功率发热器件,比如PMU(电源管理器),2G和5G的射频功放芯片等,PMU区域以及网络禁止和 IQ线重叠,即使IQ走线和PMU之间有地平面隔离也是禁止的,因为PMU开关节点造成的磁耦场耦合也会造成de-sense问题。

IQ线走线注意哪些点?

IQ线的走线要求比较严格,就是两个字“隔离”,要求解释如下:

1、每组4根走在一起,P和N一对走一起,然后4根线包GND,如下图所示,不过有些公司要求更严格,把P和N两根单独包GND;

2、IQ线上下方也要求不能有非GND的线穿过(包括焊盘),保证上下方也有GND环绕的立体包GND效果;

如下图所示,这个1个8层1阶板,IQ线走在TOP,下方有临层线穿过,也有非GND的2-7孔,这个是不允许,要保证临层一个完成的GND回路;

3、换层的孔也要保证GND完整,如下图所示,4个2-7孔的IQ信号没有包GND完整,需要加GND线保护起来;

IQ线比射频线好一点的地方,就是它不需要控制阻抗,就没有宽度的烦恼,直接按照最小线宽0.04mm走就可以了。